Introduction

ARM is a 32-bit reduced instruction set computer (RISC) instruction set architecture (ISA) developed by ARM Holdings.

It was named the Advanced RISC Machine, and before that, the Acorn RISC Machine.

The ARM architecture is the most widely used 32-bit instruction set architecture in numbers produced.

Originally conceived by Acorn Computers for use in its personal computers, the first ARM-based products were the Acorn Archimedes range introduced in 1987.

The relative simplicity of ARM processors makes them suitable for low power applications.

As a result, they have become dominant in the mobile and embedded

electronics market, as relatively low-cost, small microprocessors and

microcontrollers.

In 2005, about 98% of the more than one billion mobile phones sold each year used at least one ARM processor.

As of 2009, ARM processors account for approximately 90% of all

embedded 32-bit RISC processors and are used extensively in consumer

electronics, including personal digital assistants (PDAs), tablets,

mobile phones, digital media and music players, hand-held game

consoles, calculators and computer peripherals such as hard drives and

routers.

(source: Wikipedia)

For those unfamiliar with the family CORTEX we give some preliminary clarifications.

In general, the main features of ARM core are:

Core 32bit

RISC architecture

Excellent relations DMips/Watt

Some years ago, ARM has launched a new generation of its core identified by the name: CORTEX

The family is divided into three subfamilies:

The

x indicates that after the letter (A, R, M) is a number that identifies in detail the core.

The ARM families are divided in three macro areas, see below.

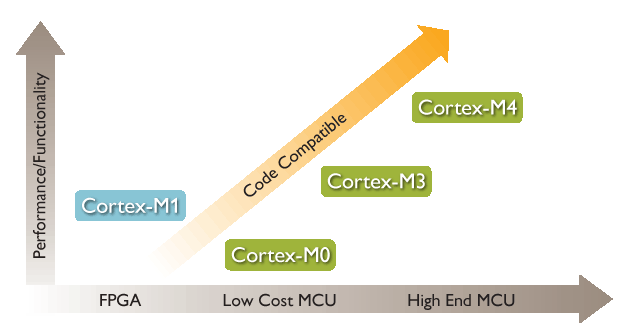

In this page we will highlight the Cortex Mx family

In this page we will highlight the Cortex Mx family (Embedded Processors)

, in particular

we will analyze the M0, M3 and M4.

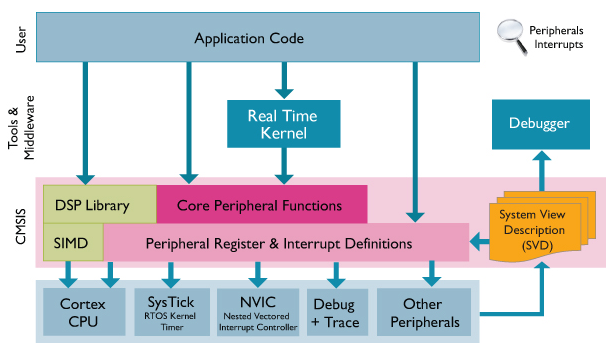

Embedded Processors are

primarily focused on delivering highly deterministic real-time

behaviour in a wide range of power sensitive applications.

These processors often execute a Real-Time Operating System (

RTOS) alongside user-developed application code, and hence only require a

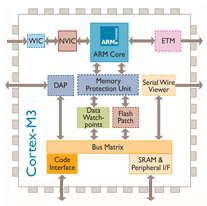

Memory Protection Unit (

MPU) as opposed to the MMU available in the Application Processors.

The

Cortex™-M0...M3 processors

have been designed to deliver industry-leading deterministic

behaviour, lowest sleep and dynamic power, and smallest area possible

whilst maintaining high processing efficiency.

The

Cortex-Rx delivers a

roadmap from Classic ARM processors including the ARM7...11™ families,

enabling existing applications to be easily ported to a higher

performance platform.

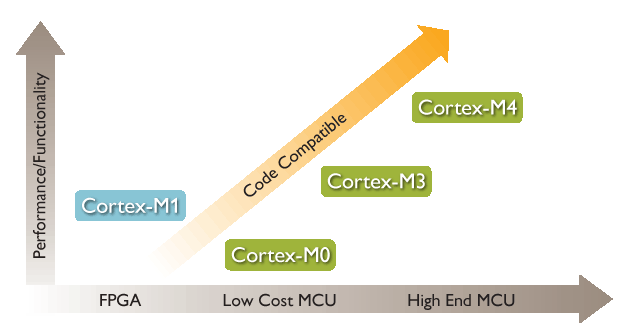

The family

CORTEX Mx is divided into four subgroups that are:

M0,

M1,

M3 and

M4.

The computing power of CORTEX Mx is in the range from

0.84 DMips/MHz to

1.25 DMips/MHz.

ARM consider obsolete the families: ARM7, ARM9 and ARM11.

Parts Cost

It is no secret that ARM Cortex M family are pushing the price/performance ratio to heretofore unseen levels.

The main target of comparison between ARM Cortex M family is traditional 8 and 16 bit microcontrollers.

Long considered the cheapest mainstream alternative, 8 bit

microcontrollers are facing considerable competitive pressure from ARM

Cortex M family.

In general, when the pin-out of the 8/16 bit MCUs are close to 28/32, it should be evaluated also at the CORTEX M family.

STM and NXP Cortex M3 price is under 1$ for 10Kps.

The Cortex Mx core, instructions & Compatibility

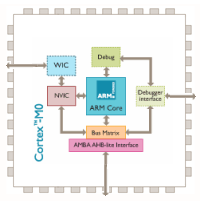

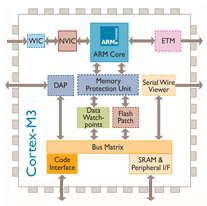

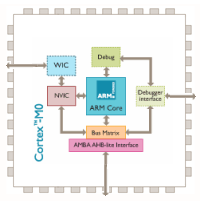

Below there are the M0, M3 and M4 core.

Below there is the instruction set concerning M0, M1, M3, M4 and M4F.

As you see there are a complete binary compatibility.

Performances & differences from M0, M1, M3 and M4 core

Performance

Code size

Differences from M0, M3 and M4